GETBIT3 macro

stx port ; Clock pulse

sty port ;

cpy port ; if Databit is 0, then Carry clear, else set.

rol

endm

Very cool indeed...Branchless, and 4 cycles per bit quicker... I NEVER would have spotted that one!!

GETBIT3 macro

stx port ; Clock pulse

sty port ;

cpy port ; if Databit is 0, then Carry clear, else set.

rol

endm

GETBIT macro

stx port ; Clock pulse

sty port ;

asl ; Shift incoming data to make space for new bit

bit port

bmi !skip ; Bmi is reversed

ora #1

!skip

endm

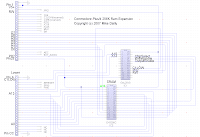

I've been playing with a cool little design for an MMC card reader on the C64, mainly so I can understand it and then try it out on the Plus/4. I've had to modify it a little as I dont have the chip he's using, but it should still work okay.

I've been playing with a cool little design for an MMC card reader on the C64, mainly so I can understand it and then try it out on the Plus/4. I've had to modify it a little as I dont have the chip he's using, but it should still work okay.

CLOCK PORT

+--+--+

GND | 1| 2| VCC (+5V)

+--+--+

/INT | 3| 4| /SPARE_CS

+--+--+

/RTC_CS | 5| 6| /PWR_BAD

+--+--+

/IORD | 7| 8| /IOWR

+--+--+

A3 | 9|10| A2

+--+--+

A1 |11|12| A0

+--+--+

D7 |13|14| D6

+--+--+

D5 |15|16| D4

+--+--+

D3 |17|18| D2

+--+--+

D1 |19|20| D0

+--+--+

GND |21|22| /RESET

+--+--+

Connection to C64 Expansion Port

---------------------------------

Clock Port Signal | Expansion Port Signal

-----------------------------------------------------

GND <=> GND (22 and Z, not 1 and A)

VCC <=> +5V (2 and 3)

/INT <=> /NMI

A0-A3 <=> A0-A3

D0-D7 <=> D0-D7

/RESET <=> /RESET

I decided to see if normal games would actually RUN with the expansion installed, so I connected the last address line needed and wrote a special uploader for it, then modified XeO3 to use the RAM expansion instead of normal RAM, and here you go! It runs fine! No difference at all!

I decided to see if normal games would actually RUN with the expansion installed, so I connected the last address line needed and wrote a special uploader for it, then modified XeO3 to use the RAM expansion instead of normal RAM, and here you go! It runs fine! No difference at all!

sei

lda #$ff

sta $fdda ; Enable Upper and Lower external banks

/WRITE = A15* /A14* PH2* /RW ; WRITE Enable (32-48k)

/CS = /C1LOW* A15* /A14* PH2* RW ; Chip Select on READ access (32-48k)

+ A15* /A14* PH2* /RW ; On WRITE access (32-48k)

/OE = /C1LOW* A15* /A14* PH2* RW ; Output ENable on READ access (32-48k)